Intel time delay in delivering new chip signals a slowdown of Moore's Law

Intel, which will for a second time miss the two-year schedule for shrinking circuitry on chips, has extended the time for developing more compact chips from two to two and a half years.

The CEO of the company, whose co-founder gave the world the Moore's Law, seemed to hint at a possible slowing down in the exponential advances in semiconductor manufacturing that has delivered faster and cheaper computing and storage every two years.

"The last two technology transitions have signalled that our cadence today is closer to 2½ years than two," Intel Chief Executive Brian Krzanich said during a conference call with analysts to discuss second-quarter results.

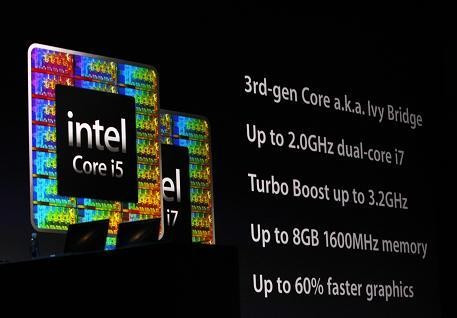

The latest chips from the Intel stable boast a 14 nanometre circuitry, or a billionth of a metre.

Intel has announced it is working on smaller 10-nanometre chips but the company was finding the going tough, according to Krzanich.

Where a two-year gap from reaching full production would suggest sometime in mid-2016, Intel announced the first 10-nanometre chips could take till the second half of 2017.

Moore's Law

Moore's Law given by Gordon Moore says that the number of transistors on a chip doubles every 18 months or so. This has held true for the last few decades with memory chips today storing around two billion times as much data as in 1965, or computing at two billion times faster speeds than back then.

But an end to this seemingly unlimited cramming of transistors on a chip has been hinted by industry watchers and experts who also suggest that more than speed in computing is required today.

The speed of computing depends on transistor density on a chip but parallel computing required in many areas calls for other tricks like graphics processing units that cut down on power consumption by assigning the right task for the right chip.

In 1999, physicist Michio Kaku declared that the "Point One barrier" (chip features 0.1 micron or 100 nanometres in size) would put an end to the transistor density, writes The Conversation.

But the 0.1 micron level was soon breached and the latest has been IBM's recent announcement of a chip with 7 nanometre features. Many suspect that Intel has already reached there, though not going public.

Krzanich maintained: "We'll always strive to get [Moore's Law] back to two years. And we'll take a look at the maturity of EUV (laser-powered extreme ultraviolet) and the maturity of the material science changes that are occurring, the complexity of the product roadmap that we're adding, and make that adjustment out in the future."

The EUV lithography tools will not be used for the 10 nm chips.

Krzanich expects Intel to remain ahead of competitors such as Samsung Electronics and Taiwan Semiconductor Manufacturing.

"We believe we'll continue to lead with roughly the same leadership position we have today," he said.

© Copyright IBTimes 2025. All rights reserved.